芯东西6月15日报道,今天,据日经亚洲报道,日本将和美国合作,最早于2025年在日本启动2nm制程国内制造基地。日经亚洲称,2nm制程的芯片可以用于量子计算机、数据中心和智能手机等产品,甚至可以决定军事装备的性能,与国家安全直接相关。尽管日本和美国计划合作攻关2nm芯片,但具备量产5nm以及下制程实力,且明确提出了2nm路线图的晶圆代工厂仅有中国台湾晶圆代工龙头台积电和韩国芯片巨头三星电子。这两家芯片制造巨头的2nm制程研究均已进入开发阶段,并提出了明确的量产时间。台积电预计将在2024年年底和2025年进行2nm制程的风险试产,量产则可能会到2025年下半年或年底。三星电子则同样计划在2025年实现2nm的量产。最近,台积电和三星电子更是在2nm制程方面动作频频。上周五,据台媒报道,台积电2nm建厂计划相关环保评审文件已送审,争取明年上半年通过,一期项目预计2024年底前投产,投资金额高达1万亿新台币(约合2268亿人民币)。而三星电子的实际负责人李在镕也访问荷兰光刻机龙头ASML,据悉目标为下一代EUV光刻机,以在2nm等先进制程上取得优势。本文将从资本支出、技术、客户争夺和制程节点等方面,呈现台积电和三星电子的全方位竞争,解析这场2nm芯片战争。本文福利:台积电、三星工艺制程向更小节点发展,竞争激烈。推荐精品报告《电子行业深度报告:晶圆代工争上游》,可在公众号聊天栏回复关键词【芯东西270】获取。

当前,全球具备5nm及以下制程芯片制造实力的晶圆代工厂只有台积电和三星电子两家。双方正展开一场以百亿美元为单位、以纳米乃至原子厚度为目标的先进制程竞赛。这种竞赛中,台积电和三星电子都投入了大量的资金,以在技术研发和产能扩充上占得先机。2021年,台积电资本支出达300亿美元,今年台积电预计资本支出将达到400-440亿美元(约合2687亿-2956亿人民币)。在2022年的投资中,台积电表示70%都将用于先进制程,10-20%用于特色工艺,10%用于先进封装。

▲台积电资本支出与营收增长对比(图片来源:Counterpoint)

在6月8日举办的股东大会上,台积电董事长刘德音预计,明年台积电资本支出仍会达到400亿美元。如果该预测为真,这这意味着台积电2021-2023年的资本支出将超过此前宣布的3年千亿美元,将达到1100亿美元-1140亿美元之间(约合7391亿-7660亿人民币)。市场分析公司Counterpoint称,台积电高额的资本支出将有很大一部分是对3nm和2nm节点产能的扩建,因为英特尔和苹果等客户可能会在2023年后带来较高的先进制程需求。相比台积电三年或超过1100亿美元的大手笔,三星电子砸起钱来也不手软。2021年,三星电子半导体与显示总资本支出达48.22万亿韩元(约合2500亿人民币),其中用于半导体的有43.57万亿韩元(约合2300亿人民币、337亿美元),主要集中在产能扩张和先进节点迁移上。

▲2018年-2020年三星电子资本支出情况(图片来源:中国台湾《工商时报》)

今年5月,三星电子宣布未来5年重大投资计划,将在2026年前,将支出增加30%以上,达450万亿韩元(约合2.4万亿人民币,3600亿美元)。据悉,虽然三星电子没有透露各业务占比,但分析师初步预计其在半导体领域将支出超千亿美元。总的来看,2021年,三星电子和台积电的资本支出超过了600亿美元,而在2017年前,全球半导体行业总支出不过700亿美元(约合4703亿人民币)。根据半导体市场分析网站IC insights的数据,2021年半导体行业资本支出合计为1520亿美元,三星电子和台积电的资本支出占比近40%。而且,这两大芯片制造巨头的资本密集度已远远超过整个半导体制造行业。

▲台积电、三星电子与IDM+代工厂商资本密集度对比(图片来源:Counterpoint)

从目前的资料来看,台积电和三星电子的2nm之战中,两家公司的进展和着重点并不相同。根据台积电2021年年报,2021年台积电已进入2nm制程研发阶段,着重于测试设备的设计与实践、光罩制作,以及硅试产,预计2025年实现2nm的量产。在去年10月的三星电子年度代工论坛上,其也宣布进入了2nm开发阶段,同样预计2025年量产。具体来说,在2nm节点上,台积电和三星电子需要在晶体管结构、材料、光刻、互连等技术上进行创新。1、新晶体管结构:三星抢先采用纳米片结构,台积电2nm弃用FinFET芯片制程演进带来最直接的变化之一就是晶体管结构改变。对2nm制程来说,目前的FinFET晶体管(鳍式场效应晶体管)结构已经不再适用,由于栅极氧化层过薄,会产生量子隧穿等效应,加剧晶体管漏电现象。在去年12月的中国集成电路设计业2021年年会上,台积电(中国)总经理罗振球称,台积电将在2nm节点推出纳米片(Nanosheet,MBCFET)晶体管架构,并采用新的二维材料。

▲从纳米片到CEFT的晶体管结构路线图(图片来源:IMEC)

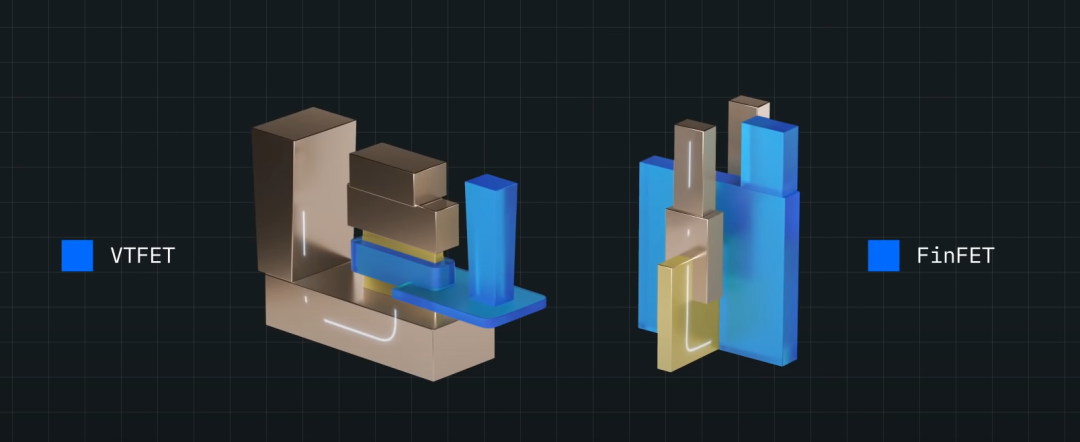

纳米片晶体管是基于纳米线晶体管(Nanowire,GAAFET)的一种晶体管结构。其纳米片的四个侧面都是栅极,比FinFET晶体管结构能更好地控制漏电电流。本月,美媒EE Times采访了台积电业务发展副总裁Kevin Zhang,称台积电正在评估MBCFET等基于纳米片的晶体管结构。不过他提到该晶体管结构只是台积电的选项之一,并不能确认什么时候用于生产。与台积电相比,三星电子在晶体管结构上更加激进,其在3nm制程上就选用了台积电用于2nm制程的MBCFET晶体管结构,还与IBM联合推出了一种新的垂直晶体管架构VTFET。在同等功率下,VTFET晶体管提供了FinFET晶体管2倍的性能,而在等效频率下,VTFET可以节省85%的功率。

▲IBM/三星电子的VTFET晶体管结构和FinFET晶体管结构对比(图片来源:IBM)

台积电Kevin Zhang谈道,台积电正在研究的新材料包括二硫化钨(WuS2)和碳纳米管等二维材料。这些二维材料能够更有效地移动电子,并让芯片实现更节能的计算。他总结称,由于摩尔定律的重要性正在减弱,芯片的能源效率和低功耗将成为未来的新基准。和晶体管结构的变化类似,二维材料的应用也是为了解决晶体管微缩后带来的量子效应,解决漏电发热、提升芯片能耗,并减小芯片面积。相比于当前的硅材料,二维半导体材料天生更适用于2nm及之后的先进制程,二硫化钨和碳纳米管是目前最具代表性的二维材料。

▲二硫化钨等r-TMD化合物薄膜的结构(图片来源:Nature)

除了晶体管结构和材料,光刻与互连技术也是实现2nm制程的关键。3、新设备:聚焦High-NA EUV光刻机,三星李在镕亲自到访ASML在光刻方面,台积电年报写道,其正在提升极紫外(EUV)光刻机的应用、降低材料缺陷并增进平坦化能力以支援2nm的制程开发。对于EUV光刻机,新的高数值孔径(High-NA)光刻机被视作2nm制程的关键。IMEC(比利时微电子研究中心)与荷兰光刻机巨头ASML共同开设了一个联合High-NA实验室,对High-NA EUV光刻机进行攻关。

▲ASML Twinscan EXE:5000系列High-NA EUV光刻机(图片来源:ASML)

如果新一代EUV光刻机研发成功,其提升将比光刻机从干式转向浸没式还要大。根据IMEC的数据,从干式到浸没式,光刻波长193nm的ArF光刻机的孔径大小相当于增加了45%,而EUV光刻机的数值孔径从0.33NA变为0.55NA,其孔径大小增加了67%,有望实现8nm的分辨率。下一代EUV光刻机也是三星电子攻关2nm制程的关键。本月初,三星集团实际控制人、三星电子副会长李在镕到访荷兰,ASML是其中关键一站。有业内人士分析,李在镕拜访ASML的主要目的之一就是采购下一代EUV光刻机,从而在先进制程上占据优势。此外,ASML和IMEC也和光刻胶供应商以及光刻计量设备供应商共同进行材料和光学计量上的研究。4、新封装技术:互连是重点,IMEC新发背面供电关键研究先进封装方面,随着芯片制程演进和晶体管结构的改变,新的互连技术被业内视作2nm制程中降低整体电阻和RC延迟的关键。昨日,IMEC在2022年IEEE VLSI技术和电路研讨会研讨会上,展示了通过纳米硅通孔(nTSV)在埋地电源轨(BPR)上的进行背面供电。

▲IMEC纳米硅通孔研究示意图(来源:IMEC)

IMEC称,这是未来基于2nm制程的2.5D和3D芯片的关键技术,该方案将在系统层面提高芯片整体供电性能,避免受到功率密度提升和电源电压下降的影响。台积电和三星电子也十分看重互连技术对先进制程的影响,均在各自的先进封装技术中。台积电的芯片互连技术路线图更是拓展到了2035年,要在2035年前实现1μm以内的SoIC互连。

▲台积电SoIC互连路线图

在芯片代工江湖中,苹果从三星电子转投台积电成就两大科技巨头同盟的故事,一直被人所津津乐道,也凸显了头部客户对晶圆制造玩家的重要性。根据Counterpoint的数据,2021年,苹果、高通、三星电子、联发科、AMD和英伟达是采用5nm制程芯片的主要芯片设计公司,这些头部芯片设计公司也会成为台积电、三星电子2nm制程代工的主要客户。

▲2021年5nm芯片出货量份额(图片来源:Counterpoint)

从体量上来看,苹果占到了2021年5nm芯片出货量的53%,高通占24%,三星电子、联发科、AMD和英伟达则分别占5%、2%、5%和3%。当前,苹果、联发科、AMD是台积电的主要客户,三星电子芯片设计部门(S.LSI)、高通和英伟达(高通和英伟达都有部分芯片在台积电代工)的芯片主要由三星电子代工业务负责。但三星电子代工业务在芯片良率、散热等问题上表现不尽如人意。根据外媒SemiAnalysis的报道,由于三星电子基于4nm制程的Exynos 2200处理器良率表现十分之低,其GPU频率从计划的1.69GHz削减到1.49GHz,最终减少到1.29GHz。为此,三星电子代工的大客户高通和英伟达已经协商按照芯片最终产量付费,而非按晶圆付费。同时,三星电子内部的手机部门、芯片设计部门和代工部门配合并不默契,其芯片设计部门指责代工部门良率和规格造假,而手机部门则指责芯片设计部门的芯片方案性能不强、成本又高。相比之下,台积电的代工良率一直表现较好,有消息称其2nm的风险试产良率也已超过了90%。这种差距也让三星电子正在失去高通和英伟达这两个最核心的先进制程代工客户。为了转向台积电的N4工艺,高通有专门的团队进行了数月的加紧工作,推出了基于台积电N4工艺的骁龙8+。而根据爆料信息,英伟达的下一代游戏显卡(即GeForce RTX 40系列)的Ada Lovelace GPU也将采用台积电的N4工艺,不再沿用三星电子代工。

▲英伟达GeForce RTX 30系列和GeForce RTX 40系列参数对比(图片来源:SemiAnalysis)

如果三星电子后续的3nm制程不能实现反超,其2nm制程的市场前景并不乐观。此外,三星电子已经进行了多轮公司架构调整。去年12月,三星电子将原先的消费电子与移动通信两个部门合并,并同时撤换了三个部门的三位CEO,替换为了此前负责电视业务的韩钟熙和子公司三星电机的社长庆桂显。在良率问题曝光后,三星电子半导体研发中心负责人、晶圆代工高管也由存储部门的专家和高管所取代。其副总裁兼NAND开发部门Song Jae-hyuk成为半导体研发中心的新负责人,存储专家、半导体设备解决方案部门全球制造与技术设施副总裁Nam Seok-woo兼任晶圆代工制造技术中心负责人,内存制造技术中心副总裁Kim Hong-shik则负责领导代工技术创新团队。从人事变动来看,三星电子把存储部门的专家和高管看作了重整逻辑芯片制造的底牌,接下来其3nm、2nm的表现或许也将决定其能否实现“2030年成为逻辑芯片制造世界第一”的目标,乃至能否继续和台积电竞争先进制程。

5nm节点后,台积电和三星电子进入了先进制程的决赛圈,谁能取得优势,谁就能掌握半导体供应链的主动权,成为5G、人工智能、自动驾驶、高性能计算等领域的核心芯片供应商。这个恰遇2020年新冠肺炎疫情全球缺芯的先进制程之战,直接就进入了白热化阶段,三星电子和台积电不仅要在制程工艺上一决胜负,更要扩产建厂掌握供应链核心地位。这对两家公司来说,既是挑战,也是机遇。如今台积电万亿新台币晶圆厂已进入审批流程,更在先进制程产能、客户和良率等方面取得了领先。但三星电子仍不会放弃这场逼近物理极限的战争,将在3nm之后和台积电一决胜负。本文福利:台积电、三星工艺制程向更小节点发展,竞争激烈。推荐精品报告《电子行业深度报告:晶圆代工争上游》,可在公众号聊天栏回复关键词【芯东西270】获取。